More about DDR4 at Why migrate to DDR4?

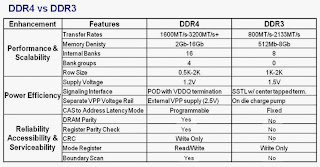

- "Improved capacity and performance scalability:

- Improved power efficiency:

- Improved reliability, availability and serviceability (RAS):

DDR4 SDRAM specification improves RAS is that DDR4 device supports command and address parity error detection, as well as recovery from parity error...supports a connectivity test mode, so that a system controller can test and detect connectivity faults without needing to go through DRAM initialization sequencing...The DDR4 register also provides enhanced RAS over the DDR3 register in that the DDR4 register can be configured to support command blocking upon detection of a parity error.."

It will still be awhile before DDR4 will replace DDR3.

Ron

Insightful, timely, and accurate semiconductor consulting.

Semiconductor information and news at - http://www.maltiel-consulting.com/

Kristin Lewotsky

10/17/2013 10:30 AM EDT

After seven years of development, JEDEC released the DDR4 DRAM standard (JESD79-4) last fall. The standards committee recognized the ever-increasing performance demands placed on memory and knew that a simple update wouldn't be enough.

The DDR4 architecture represents a major departure from that of previous DRAM standards, affording significant performance improvement, dramatic reductions in power demand, and compatibility with 3D architectures. Typically, a couple of years elapses between the release of a standard and broad availability of product.Given the rapid evolution of the technology, however, DDR4 is expected to mature quite a bit more rapidly than its predecessors, with broad deployment hitting in 2014. Indeed, at the recent Intel Developers Forum (IDF), companies demonstrated working systems, like Kingston Technology's memory demo highlighting 192 GB of working 2133 MT/s DDR4 Registered DIMMs at 1.2V operating on a future Intel reference platform. We thought it was a good time to take a look at some of the offerings out on the market available to design engineers.

The following slideshow reveals that the products curently sampling go beyond memory modules to include controllers and chipsets.

SDRAM controller and PHY (Altera)SDRAM controller and PHY (Altera)

A DDR4 SDRAM interface solution provides a flexible method for designers to interface external memory with FPGAs and SoCs. The Altera PHY megafunctions and associated High-Performance Memory Controller II (HPMCII) are two distinct offerings that can be used together or individually. The PHY megafunctions provide the interface between the memory controller and the external memory devices, performing read and write operations to memory. It can be used as part of the HPMCII MegaCore function to create a complete controller and PHY solution for DDR4 SDRAM, or they can be used separately with a custom controller.

DDR4 DRAM (Micron)DDR4 DRAM (Micron)

Micron's 8 Gb DDR4 DRAM operates at data rates as high as 2400 MT/s. By leveraging the power saving options enabled by the DDR4 standard, the devices deliver a 40 percent reduction in power consumption and 20 percent reduction in voltage compared to DDR3 DRAM. The components also sport a JTAG boundary scan feature to enable early fault detection during testing. At the 2013 Consumer Electronics Show, Micron's consumer line Crucial announced availability of DDR4 DRAM modules, although they do not appear currently on the company's website.

PHY IP (Synopsys)

A set of mixed-signal PHY IP cores provides a physical interface compliant to the DDR4 spec, as well as to LPDDR3 and prior editions. The Synopsys DesignWare DDR4 multiPHY IP supports DDR4 SDRAM speeds up to 2400 Mbps. Each DDR4 multiPHY encompasses an application-specific SSTL I/O library, a single address/command macro block, multiple-byte-wide data macro blocks instantiated as required to accommodate the memory channel width, and separate PLL macrocells that directly abut the address/command macro block and data macro blocks. They target 28-nm nodes and below.

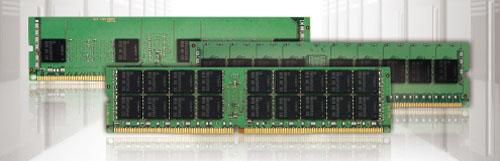

Enterprise-class RDIMM (Innodisk)Enterprise-class RDIMM (Innodisk)

Innodisk a step toward the server market with the sampling of DDR4 RDIMMs. The family includes 4 GB, 8 GB, and 16 GB devices. Memory bus speeds start at 2133 MHz. With DDR4, the maximum capacity per chip has now been doubled from 64 GB to 128 GB. The higher memory densities possible with DDR4 will save space, simplify module construction, and improve internal airflow.

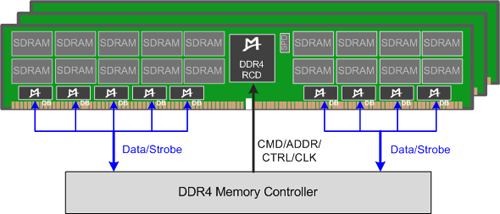

LRDIMM chipset (IDT)LRDIMM chipset (IDT)

This chipset for DDR4 RDIMMs and LRDIMMs combines IDT's 4DB0124 DDR4 data buffer and its 4RCD0124 registered clock driver (RCD) to provide complete buffering of command, address, clock, and data signals across an LRDIMM. Instantiating nine data buffers across the bottom of an LRDIMM with a single RCD in the center allows up to 16 ranks of DRAM to be reduced to a single load, minimizing stub lengths and physical skew between data bits and increasing the speed and bandwidth performance of LRDIMMs in multi-slot systems. The 4DB0124 supports advanced configuration and power interface (ACPI) states, which IDT claims reduces overall system power consumption.

DDR4 registering clock driver (Montage)DDR4 registering clock driver (Montage)

A dual-mode DDR4 registering clock driver (RCD) designed for next-generation server platforms can be used independently on an RDIMM or in conjunction with nine data buffers on an LRDIMM. With a variety of power-saving modes such as S3 low power mode, CK Stop mode, etc., the M88DDR4RCD01 from Montage Technology supports 1.2V VDD operations. It features a configurable 32-bit 1:2 registering buffer for address and control signals and I2C interface support.

DDR4 DRAM (Samsung)DDR4 DRAM (Samsung)

Samsung is taking aim at the enterprise server market with volume release of this family of 4 Gb DDR4 DRAM. Fabricated using 20-nm process technology, the devices deliver 2,667 Mbps operation, a factor of 1.25 greater than the company's 20-nm-class DDR3, all-consuming 30 percent less power. Current packaging includes a 78-ball BGA.

DDR4 register (Inphi)DDR4 register (Inphi)

A 0.95 JEDEC-compliant DDR4 register targeted at enterprise and IP data center supports up to DDR4-2666 memory. Inphi demonstrated its iDDR4RCD-GS02 at the Intel Developers' Forum, running a test system at speeds up to 2400 MT/s while consuming less power than DDR3-1866 modules of the same capacity. The register allows system designers to customize performance and power profile across a wider range of operating frequencies as compared to DDR3.

No comments:

Post a Comment