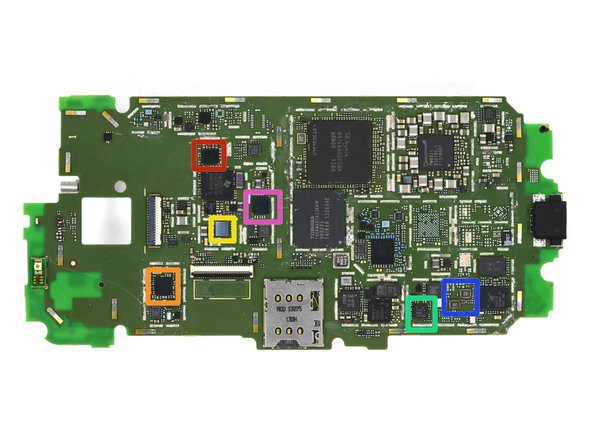

The key chips in Moto X are listed below.

Ron

Insightful, timely, and accurate semiconductor consulting.

Semiconductor information and news at - http://www.maltiel-consulting.com/

Motorola Moto X Teardown

Step 1 — Motorola Moto X Teardown

- The love child of Motorola and Google is here, and we are dying to crack open the little Motoroogle.

- Technical Specifications:

- Dual-core 1.7 GHz Qualcomm Snapdragon S4 Pro processor

- 2 GB RAM

- 4.7-inch 1280x720 pixels AMOLED display

- 16 or 32 GB internal storage

- Qualcomm Adreno 320 GPU

- .........

Step 9

- Motorola claims the Moto X battery can power through an amazing 24 hours of "mixed usage."

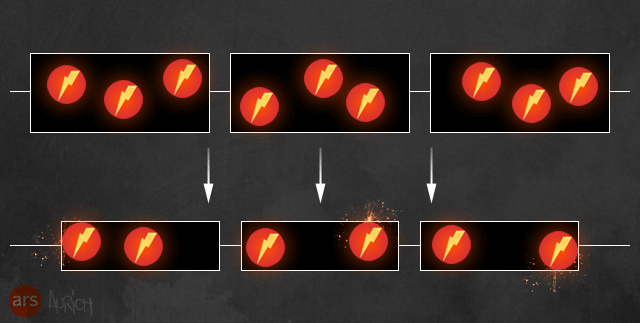

- How does the Moto X accomplish such a feat with a 3.8 volt, 2200 mAh Lithium ion battery? The secret is in the X8 Mobile Computing System.

- The Motorola X8 Mobile Computing System is comprised of a Qualcomm Snapdragon S4Pro family processor, a natural language processor and a contextual computing processor.

- Motorola developed a custom system architecture, which, when coupled with eight processor cores, allows for the delegation of processing power:

- 4 graphics processor cores for "stunning clarity"

- 2 application processor cores for "swift action"

- 2 low-power cores—"awaiting your next command"

Step 10

- Out comes the upper midframe panel, housing the speaker, headphone jack, more antennas, and pressure contacts.

- Yay, pressure contacts! We like spring pressure contacts because they don't require any work to disconnect.

- This is possibly the most modular headphone jack we've ever seen. It pops right out of the upper midframe panel, spring contacts and all.

10 MP rear-facing camera- Notable ICs on the motherboard:

- SK Hynix H9TKNNNBPDAR RAM (we assume that the Snapdragon S4 Pro is also layered under this IC)

- NXP 44701 NFC Chip

- Skyworks 77619-12 Multiband Multimode Power Amplifier Module for Quad-Band GSM / EDGE and Penta-Band (Bands I, II, IV, V, VIII) WCDMA/ HSDPA/ HSUPA/ HSPA+/ LTE

- Additional ICs:

- 0V00660 A56G 1B