There is a room for an overall personal computer hierarchy reorganization. Maybe Apple could lead here.

Currently in PC/ Mac we have a microprocessor (with some fast DRAM memory) connected to long term storage in flash SSD or HDD.

There would be many benefits to adding a small flash NAND between the microprocessor and the long term storage. Such computer hierarchy would benefit from the faster operation of the small flash NAND storage and its long term non volatile storage. It will also reduce power consumption.

The NAND memory could support the microprocessor operations or be used for storage of the operating system.

There were rumors a couple of years ago about Intel working on such system. It never made it out due to legacy software optimization issues.

Ron

Apple likely to use NAND storage in upcoming MacBook Pros, analyst says

http://www.appleinsider.com/articles/12/05/30/apple_likely_to_use_nand_storage_in_upcoming_macbook_pros_analyst_says.html

By Mikey Campbell

Published: 05:35 PM EST (02:35 PM PST)

A research analyst from Barclays believes that Apple's success in NAND adoption will drive the company to use the technology in a rumored refresh of its MacBook Pro line, a move that will disrupt the business of of both hard drive and PC makers.

In a note to investors released on Wednesday, Ben Reitzes of Barclays Equity Research said that the adoption rate of Apple devices using SSDs, along with a continuing move to cloud computing, will push consumer laptop demand toward flash-based storage.

Perhaps the single greatest setback to flash adoption is that the price of solid state solutions grossly outweigh comparable HDDs, keeping the technology out of reach for everyday consumers. This cost ratio may tilt in the physical hard drive's favor, however consumers have recently started giving up storage space and low cost for design and performance benefits, evidenced by the success of the thin and light MacBook Air.

Reitzes believes that the advent of cloud computing will help ease consumers in the transition from physical drives to flash by offloading storage to servers, thus diminishing the need for pricey high-capacity NAND drives. Apple's iCloud is already well in-place and has the potential of filling offsite storage needs if the company chooses to move to a NAND-heavy laptop lineup.

For these reasons, the analyst expects Apple to reveal a NAND-equipped MacBook Pro as well as MacBook Airs with increased storage options in the near future.

"We believe these products combined can ramp quarterly demand for Macs by up to 1 million incremental units on a run rate basis - taking over a point of share from HDD-based PCs," Reitzes said.

He goes on to say that an estimated 5 to 10 percent of notebook PC sales have been cannibalized by NAND-carrying iPads and iPhones, further impacting HDD demand for PCs. The move to portable products has been dubbed as the "post-PC era," as consumers begin to replace computers with tablets and handset. Interestingly, this trend toward flash in consumer devices is seen as fueling data growth, which helps to augment sales of enterprise-class HDDs.

Commentary on Semiconductor industry at the confluence of Process, Product, and Circuits design

Contact Info.

Semiconductor Information and Business News at http://maltiel-consulting.com/

mailto:ron@maltiel-consulting.com

Phone / Fax : (408) 446 - 3040

mailto:ron@maltiel-consulting.com

Phone / Fax : (408) 446 - 3040

Thursday, May 31, 2012

Wednesday, May 30, 2012

Hiding Patents From Spies Cost Inventors’ Right

Congress is asking whether sensitive patent applications should be kept under wraps to protect them from economic espionage, a question that implies curbing the ability of inventors to promote their ideas globally.

Congress is asking whether sensitive patent applications should be kept under wraps to protect them from economic espionage, a question that implies curbing the ability of inventors to promote their ideas globally.

Secrecy provisions have for decades been reserved for innovations with national security importance. Congress ordered the U.S. Patent and Trademark Office to consider whether similar restrictions should apply to inventions with implications for “economic security.”

Widening Secret Patents Seen as Costing Inventors’ Rights

By Susan Decker and Eric Engleman - May 29, 2012 9:00 PM PT .

The U.S. Patent and Trademark Office, at the direction of a House Appropriations subcommittee, is gathering information on whether certain patent applications should be kept secret.

The U.S. Patent and Trademark Office, at the direction of a House Appropriations subcommittee, is gathering information on whether certain patent applications should be kept secret. Photo: Christopher Powers/Bloomberg

Chart: Number of Secret Patents Imposed by U.S. Military .When inventors’ U.S. applications are secret, they are unable to patent their ideas in other countries. That alters a bargain, established in the U.S. Constitution, giving inventors a limited monopoly on their ideas in exchange for exposing knowledge to the world and allowing others to build on it.

“It’s ridiculous, absurd,” Bob Stoll, who ran the agency’s patent operations from late 2009 until Dec. 31, said in an interview. “We have an economically valuable patent we don’t want our companies to secure in China, in Europe, in Australia or anywhere else in the world? It flies in the face of what our country should be trying to do.”

The directive to the patent office was part of a spending bill enacted in November. The provision, added by the House Appropriations subcommittee led by Virginia Republican Frank Wolf, called for a review of whether patent secrecy should be extended to cover inventions “that could potentially impact economic security,” according to a Federal Register notice.

The patent office, which hasn’t taken a position, is collecting comments through June 19.

$398 Billion

“While PTO has a fairly defined procedure for dealing with national security patents, they haven’t strategically rethought what is sensitive patent data in the 21st century,” said Thomas Culligan, Wolf’s legislative director.

Hackers and illicit programmers in China and Russia are pursuing American technology and industrial secrets, jeopardizing an estimated $398 billion in U.S. research spending, according to a November report from the U.S. National Counterintelligence Executive.

The report called China the world’s biggest perpetrator of economic espionage and said the theft of sensitive data in cyberspace is accelerating. Areas cited as most targeted include pharmaceuticals, information technology, military equipment and advanced materials and manufacturing processes.

Forfeited Rights

Along with examining whether expanded patent secrecy is a good idea, the patent office is also asking who would be responsible for identifying applications to be kept under wraps, what criteria would be used, and what types of inventions would qualify. It also has to look at how it would affect inventors’ ability to obtain patents outside the U.S.

Applications usually are made public after 18 months, a standard followed in most developed nations. If applications are kept secret, at the inventor’s request or by U.S. determination, the owners can’t seek patents in other countries.

“There would be challenges relative to treaty obligations that we have, and those would have to be worked out,” David Kappos, director of the patent office, told a House Judiciary subcommittee on May 21.

There were 5,241 secrecy orders in effect in fiscal 2011, most established by the Defense Department, according to a patent office report given to the Federation of American Scientists, a non-partisan agency founded by the developers of the Manhattan Project to research issues that include reducing threats from nuclear, biological and chemical weapons.

Some inventions can remain secret for decades. One application for a radar system developed by the Navy in 1948 didn’t become a patent for 45 years.

Patent Vault

The patent office looks for key words in applications to determine if something might be of interest, and passes those applications to the Army, Air Force, Navy and other defense agencies. If flagged, the applications are reviewed by examiners with security clearances and placed in a vault, with an annual review by the defense agencies to see if the secrecy order can be lifted and a patent issued.

There’s no appeal if an application is declared a secret, although some owners can get compensation if they can prove the invention has market value. Some applications are so sensitive that they’re sealed with access only to defense agencies, said Paul Fucito, a patent office spokesman.

‘You’re Stuck’

“No applicant is very happy about having their application placed under a secrecy order,” said Don Pelto, a patent lawyer with Sheppard Mullin in Washington, whose firm represents defense companies. “There’s no way for the applicant to have that secrecy order lifted. You’re stuck. If the same stuck-ness applies to this potential new rule, applicants are in a heap of trouble.”

Manufacturers aren’t willing to give up foreign patents even if they are tipping off rivals or counterfeiters, said Stoll, now a lawyer at Drinker Biddle & Reath LLP in Washington.

“Commercial espionage is rampant and everyone’s trying to get a leg up on the leaders in the market,” he said. “But secret patent applications are fraught with peril and would harm the United States in the long run.”

It takes, on average, 34 months to complete an application, or 16 months after it’s made public, and even longer in semiconductors or electronics. Wolf is concerned that foreign entities could use that gap to get information that would put the U.S. at an economic disadvantage, Culligan said in an interview.

“It may be some cutting-edge technology, game-changing technology, and we’re exposing it at 18 months with no protections,” Culligan said.

Published Applications

Websites are dedicated to gleaning the next Apple Inc. (AAPL) or Google Inc. (GOOG) product based on their published applications, and rival companies routinely check patents to see what the competition is up to.

“No one knows if what’s in a published patent application is going to be a blockbuster -- it takes marketing and skill,” Pelto said. “Nearly every patent applicant is hoping their invention becomes economically significant. That’s part and parcel of the patent procedure in the U.S.”

Economic espionage is mostly aimed at technology and business strategy earlier than the patent stage, Willy Shih, a professor of management practice at Harvard Business School who studies industrial competitiveness, said in an interview.

“The much more interesting stuff, the really good stuff, is probably not patented yet,” Shih said, calling patents a trailing indicator of economically valuable data.

Trade Secrets

Relying on legal protections for trade secrets, in which inventions aren’t patented, is one route for companies that don’t want to expose their inventions to rivals.

DuPont Co., which kept trade secrets related to the manufacture of Kevlar, an anti-ballistic fiber used in police and military gear, accused Korea’s Kolon Industries Inc. of stealing that information, winning a $919.9 million jury verdict last year against the company.

Expanded patent secrecy won’t stop economic espionage because foreign hackers are penetrating corporate computer networks to steal information, Rick Holland, a Dallas-based information-security and risk analyst with Forrester Research Inc., said in an interview.

“It’s a lose-lose,” Holland said. “It’s not effective and is putting organizations in a bad spot.”

Labels:

Circuit,

circuit expert,

circuit experts,

evidence,

expert,

forensic,

judicial,

judiciary,

juridical,

justiciary,

legal,

litigation,

patent,

suit,

testify,

trade secret,

USPTO,

witness

Thursday, May 17, 2012

Flash, DRAM Memory Impact Smartphone Design

Reducing power consumption and heat production is key for long operation time of battery between charges. Memory chip design plays a major role in increasing it. The article below discuss three different approaches to achieve long battery life.

Ron Maltiel

Semiconductor memory plays a large role in smartphone design says Matti Floman of Nokia | Denali Memory Report

http://denalimemoryreport.wordpress.com/2012/05/16/semiconductor-memory-plays-a-large-role-in-smartphone-design-says-matti-floman-of-nokia/

“There’s no real difference between PCs and mobile phones today,” said Matti Floman from Nokia who gave the first keynote speech at last week’s JEDEC Mobile Forum. There is no difference in the types of applications run; there’s no difference in performance; there’s no difference in connectivity. Because smartphones now offer the sort of universal, run-any-app abilities of PCs, they are rapidly moving down the phone hierarchy, penetrating the broad mobile phone subscriber market and pushing out phones with lesser abilities such as feature phones.

Although user expectations are not different between PCs and phones, there’s certainly a difference in terms of hardware design. It’s not easy to make powerful memory that doesn’t consume lots of power, said Floman. In addition, phones need to fit more and more memory capacity into smaller and smaller volumes to make room for more battery in the phone—to accommodate users’ desire for more time between battery charges. Smartphone form factors are also evolving, said Floman. The favored form factor these days is a thin phone with a large display.

Semiconductor memory requirements to accommodate these design characteristics include:

■Scalability (in terms of capacity, performance, and functionality), because no one can see five years ahead

■More bandwidth

■New packages (to accommodate 3D IC assembly and thermal issues)

■Lower power consumption

■Scalable modules

■Standards

Then Floman focused on what’s really important now: power. “Power is the focus of the future,” he said. Power consumption is limited by battery capacity and the heat tolerance of stacked packages, because whether or not the mobile phone makers are using 3D IC assembly, they are already stacking die. Here’s an image Floman used to show the evolution of 3D stacking in smartphone design. Floman noted that the maximum operating temperature for NAND Flash devices is 85° C and that DRAMs are limited to 105° C. Die stacking compounds the problem of heat dissipation.

One of the most interesting slides that Floman presented at the JEDEC Mobile Forum, in my opinion, was an image that showed three processor/memory architectures for mobile phones.

The graphic looked like this:

The two architectures on the left are execute-in-place (XIP) architectures. The leftmost architecture employs pseudo-static RAM and NOR Flash as memory and executes operating-system code directly from the NOR Flash memory. The middle architecture replaces the pseudo-static RAM and NOR Flash memory with LPDDR2 SDRAM and LPDDR2-N Non-Volatile Flash memory. It’s still an execute-in-place architecture but the memory components are newer and deliver more performance with better capacity.

The architecture on the right is a shadowing architecture where the OS code is stored in a mass-storage device (NAND Flash memory) and the code is first transferred to DRAM and then executed. High-end smartphones use this architecture.

These architectural designs will hold unless a new type of memory with both fast read/write times and non-volatile storage become commercially available in the required capacities and the required cost per bit. If that happens, the smartphone will only need one memory type—perhaps that might be magnetic RAM (MRAM) or Memristor-based memory. But that’s not the situation today.

The best possible performance, said Floman, will come from Wide I/O DRAM while the UFS (Universal Flash Storage) standard appears to be poised to become the next commonly used storage medium for smartphone design. UFS “will be the next generation mass memory” for smartphones, said Floman.

All of this evolution has but a single purpose. “You will not buy your next phone from the same manufacturer unless it provides new functions,” Floman said as he concluded his keynote speech.

Ron Maltiel

Semiconductor memory plays a large role in smartphone design says Matti Floman of Nokia | Denali Memory Report

http://denalimemoryreport.wordpress.com/2012/05/16/semiconductor-memory-plays-a-large-role-in-smartphone-design-says-matti-floman-of-nokia/

“There’s no real difference between PCs and mobile phones today,” said Matti Floman from Nokia who gave the first keynote speech at last week’s JEDEC Mobile Forum. There is no difference in the types of applications run; there’s no difference in performance; there’s no difference in connectivity. Because smartphones now offer the sort of universal, run-any-app abilities of PCs, they are rapidly moving down the phone hierarchy, penetrating the broad mobile phone subscriber market and pushing out phones with lesser abilities such as feature phones.

Although user expectations are not different between PCs and phones, there’s certainly a difference in terms of hardware design. It’s not easy to make powerful memory that doesn’t consume lots of power, said Floman. In addition, phones need to fit more and more memory capacity into smaller and smaller volumes to make room for more battery in the phone—to accommodate users’ desire for more time between battery charges. Smartphone form factors are also evolving, said Floman. The favored form factor these days is a thin phone with a large display.

Semiconductor memory requirements to accommodate these design characteristics include:

■Scalability (in terms of capacity, performance, and functionality), because no one can see five years ahead

■More bandwidth

■New packages (to accommodate 3D IC assembly and thermal issues)

■Lower power consumption

■Scalable modules

■Standards

Then Floman focused on what’s really important now: power. “Power is the focus of the future,” he said. Power consumption is limited by battery capacity and the heat tolerance of stacked packages, because whether or not the mobile phone makers are using 3D IC assembly, they are already stacking die. Here’s an image Floman used to show the evolution of 3D stacking in smartphone design. Floman noted that the maximum operating temperature for NAND Flash devices is 85° C and that DRAMs are limited to 105° C. Die stacking compounds the problem of heat dissipation.

One of the most interesting slides that Floman presented at the JEDEC Mobile Forum, in my opinion, was an image that showed three processor/memory architectures for mobile phones.

The graphic looked like this:

The two architectures on the left are execute-in-place (XIP) architectures. The leftmost architecture employs pseudo-static RAM and NOR Flash as memory and executes operating-system code directly from the NOR Flash memory. The middle architecture replaces the pseudo-static RAM and NOR Flash memory with LPDDR2 SDRAM and LPDDR2-N Non-Volatile Flash memory. It’s still an execute-in-place architecture but the memory components are newer and deliver more performance with better capacity.

The architecture on the right is a shadowing architecture where the OS code is stored in a mass-storage device (NAND Flash memory) and the code is first transferred to DRAM and then executed. High-end smartphones use this architecture.

These architectural designs will hold unless a new type of memory with both fast read/write times and non-volatile storage become commercially available in the required capacities and the required cost per bit. If that happens, the smartphone will only need one memory type—perhaps that might be magnetic RAM (MRAM) or Memristor-based memory. But that’s not the situation today.

The best possible performance, said Floman, will come from Wide I/O DRAM while the UFS (Universal Flash Storage) standard appears to be poised to become the next commonly used storage medium for smartphone design. UFS “will be the next generation mass memory” for smartphones, said Floman.

All of this evolution has but a single purpose. “You will not buy your next phone from the same manufacturer unless it provides new functions,” Floman said as he concluded his keynote speech.

Wednesday, May 16, 2012

Intel Roadmap to 2015 and Beyond: 5nm Technology

Intel discussed roadmap to 2015 at their annual Investor meeting day on the 10th of May 2012 in Santa Clara.

Topic mentioned included the roadway to 5nm process, 450 mm wafers. See more below.

Ron

Intel Roadmap to 2015 and Beyond: 5nm Technology, Merrifield Mobile Processor, Microservers and More

http://www.cnx-software.com/2012/05/15/intel-roadmap-to-2015-and-beyond-5nm-technology-merrifield-mobile-processor-microservers-and-more/

Intel had their annual Investor meeting day on the 10th of May 2012 in Santa Clara where we would learn a few things about what's ahead for Intel and the semiconductor industry. Paul Otellini, Intel President and Chief Executive Officer, started the meeting by giving some numbers about Intel results and showing opportunities existing for cloud and data center, personal computing, mobile devices and intelligent systems (for automotive, retail and communications markets). One interesting point was the tremendous growth in data Intel expects from 2,500 Exabytes per year (7 EB/day) today to 8,000 Exabytes by 2015 which the majority of the growth lead by Big data. He also boasted about Intel technology advantage. For example, Intel introduced High-K Metal Gate technology in 2007 and competitor only got it in products last year (btw Samsung Exynos 5 uses HKMG). They recently introduced Tri-gate technology and they only expect competitors to catch up within 4 years. Finally one of the slide (see below) shows that Intel intends to be able to manufacture silicon using 10 to 5nm technology sometimes after 2015.

The technology to achieve this feat is still at the fundamental research stage however. You can read the presentation (PDF) for more details.

Kirk Skaugen, General Manager of the PC Client Group, mainly talked about Ultrabooks which are high-performance, expensive (700 USD up) and thin notebooks. Intel Haswell Processor is designed to power Ultrabooks (in 2013) able to get 10 days of connected standby providing 20 times more efficiency than Intel iCore 5 device available in 2011. If you want to know more about the future for Intel based PC, Laptop and Ultrabook, you can read the presentation.

Diane Bryant, Vice President & General Manager of the Datacenter & Connected Systems Group, mainly talked about high end servers, but there is also a small section about microservers showing Xeon processors (Ivy Brigde) consuming 17W and the lower-end Atom Centerton SoC consuming a mere 6W. You can download the PDF presentation to know more about Intel datacenter and cloud solutions, customers and prospects.

Now let's move to smartphones and tablets with Hermann Eul & Mike Bell of Intel Mobile and Communications Group. They started by showing Intel technological know-how for mobile applications and Intel R&D commitment with over 3,000 engineer working on software for Windows, Linux (Intel is No. 2 contributor) and other operating systems, including 1,200 working on Android for mobile.

Then they gave some details about Atom Medfield processor, their first smartphone processor, which can be integrated into smartphones that support 8MPixel camera, 1080p video via HDMI and last 14 days on a single battery charge (using a 1460mA battery). They also mentioned Anandtech article showing Medfield based Lava XOLO X900 beats the competition in terms of performance (for some benchmarks) and matches the power consumption of existing smartphones.

They also showed their smartphone platform roadmap with processors for both the high end and lower end segments of the market.

At the higher-end, we would get:

*Intel Atom Z2580 with Intel XMM 7160 LTE + 2X HSPA+ providing twice the performance of Medfield.

*Merrifield processor with XXM 7260 using 22nm manufacturing process.

and the lower-end:

*Intel Atom Z2000 @ 1GHZ with XMM 6265 (HSPA+)

*Intel Atom 6331 (22nm)

as well as future processors based on 14nm technology.

Intel also provided their tablet roadmap with Clover Trail 1.8 GHz 32nm processor (2012), Bay Trail 22nm processor (2013) and next generation processor (no name yet) using 14nm process (2014).

Have a look at the presentation for more information.

Brian Krzanich, Chief Operating Officer, gave a presentation about manufacturing and fabs which I would not normally mention in this blog, were it not for this slide:

Currently, silicon Fabs use 200mm wafers which requires company to generate 3 to 5 billions in revenue to stay afloat representing all companies in the chart above (Elpida recently filled for bankruptcy before being bought by Micron). Now some companies starts to move to 300mm. A manufacturing site designed for this type of wafer requires 9 to 12 billions in revenues (shown in green above), but as it scales it becomes much more cost effective than a 200mm wafer Fab. That means that companies such as Freescale, NXP Broadcom and AMD would eventually have to go Fabless to survive, be bought or go bankrupt. After 2015, Fabs designed for 450mm wafer will start to show up (I'm pretty sure there is a mistake on the slide above and "300mm Fab" should read "450mm Fab"). This type of Fab requires 15 billions in revenues according to Intel, which would means that only 2 or 3 companies in the world, namely Intel, Samsung and possibly TSMC will be large enough to have manufacturing sites, unless companies such as Texas Instruments and Toshiba buy smaller players in the meantime.

If you are interested, you can check the PDF.

There were also two other presentations by the sales team and the CFO. You can listen to the webcast and access all the presentation slides on Intel Corporation 2012 Investor Meeting

Topic mentioned included the roadway to 5nm process, 450 mm wafers. See more below.

Ron

Intel Roadmap to 2015 and Beyond: 5nm Technology, Merrifield Mobile Processor, Microservers and More

http://www.cnx-software.com/2012/05/15/intel-roadmap-to-2015-and-beyond-5nm-technology-merrifield-mobile-processor-microservers-and-more/

Intel had their annual Investor meeting day on the 10th of May 2012 in Santa Clara where we would learn a few things about what's ahead for Intel and the semiconductor industry. Paul Otellini, Intel President and Chief Executive Officer, started the meeting by giving some numbers about Intel results and showing opportunities existing for cloud and data center, personal computing, mobile devices and intelligent systems (for automotive, retail and communications markets). One interesting point was the tremendous growth in data Intel expects from 2,500 Exabytes per year (7 EB/day) today to 8,000 Exabytes by 2015 which the majority of the growth lead by Big data. He also boasted about Intel technology advantage. For example, Intel introduced High-K Metal Gate technology in 2007 and competitor only got it in products last year (btw Samsung Exynos 5 uses HKMG). They recently introduced Tri-gate technology and they only expect competitors to catch up within 4 years. Finally one of the slide (see below) shows that Intel intends to be able to manufacture silicon using 10 to 5nm technology sometimes after 2015.

Intel Manufacturing Technology Road Map

The technology to achieve this feat is still at the fundamental research stage however. You can read the presentation (PDF) for more details.

Kirk Skaugen, General Manager of the PC Client Group, mainly talked about Ultrabooks which are high-performance, expensive (700 USD up) and thin notebooks. Intel Haswell Processor is designed to power Ultrabooks (in 2013) able to get 10 days of connected standby providing 20 times more efficiency than Intel iCore 5 device available in 2011. If you want to know more about the future for Intel based PC, Laptop and Ultrabook, you can read the presentation.

Diane Bryant, Vice President & General Manager of the Datacenter & Connected Systems Group, mainly talked about high end servers, but there is also a small section about microservers showing Xeon processors (Ivy Brigde) consuming 17W and the lower-end Atom Centerton SoC consuming a mere 6W. You can download the PDF presentation to know more about Intel datacenter and cloud solutions, customers and prospects.

Now let's move to smartphones and tablets with Hermann Eul & Mike Bell of Intel Mobile and Communications Group. They started by showing Intel technological know-how for mobile applications and Intel R&D commitment with over 3,000 engineer working on software for Windows, Linux (Intel is No. 2 contributor) and other operating systems, including 1,200 working on Android for mobile.

Then they gave some details about Atom Medfield processor, their first smartphone processor, which can be integrated into smartphones that support 8MPixel camera, 1080p video via HDMI and last 14 days on a single battery charge (using a 1460mA battery). They also mentioned Anandtech article showing Medfield based Lava XOLO X900 beats the competition in terms of performance (for some benchmarks) and matches the power consumption of existing smartphones.

They also showed their smartphone platform roadmap with processors for both the high end and lower end segments of the market.

Intel Smartphone Platform Roadmap

At the higher-end, we would get:

*Intel Atom Z2580 with Intel XMM 7160 LTE + 2X HSPA+ providing twice the performance of Medfield.

*Merrifield processor with XXM 7260 using 22nm manufacturing process.

and the lower-end:

*Intel Atom Z2000 @ 1GHZ with XMM 6265 (HSPA+)

*Intel Atom 6331 (22nm)

as well as future processors based on 14nm technology.

Intel also provided their tablet roadmap with Clover Trail 1.8 GHz 32nm processor (2012), Bay Trail 22nm processor (2013) and next generation processor (no name yet) using 14nm process (2014).

Have a look at the presentation for more information.

Brian Krzanich, Chief Operating Officer, gave a presentation about manufacturing and fabs which I would not normally mention in this blog, were it not for this slide:

Revenue per Company and Factory Cost Depending on Wafer Size

Currently, silicon Fabs use 200mm wafers which requires company to generate 3 to 5 billions in revenue to stay afloat representing all companies in the chart above (Elpida recently filled for bankruptcy before being bought by Micron). Now some companies starts to move to 300mm. A manufacturing site designed for this type of wafer requires 9 to 12 billions in revenues (shown in green above), but as it scales it becomes much more cost effective than a 200mm wafer Fab. That means that companies such as Freescale, NXP Broadcom and AMD would eventually have to go Fabless to survive, be bought or go bankrupt. After 2015, Fabs designed for 450mm wafer will start to show up (I'm pretty sure there is a mistake on the slide above and "300mm Fab" should read "450mm Fab"). This type of Fab requires 15 billions in revenues according to Intel, which would means that only 2 or 3 companies in the world, namely Intel, Samsung and possibly TSMC will be large enough to have manufacturing sites, unless companies such as Texas Instruments and Toshiba buy smaller players in the meantime.

If you are interested, you can check the PDF.

There were also two other presentations by the sales team and the CFO. You can listen to the webcast and access all the presentation slides on Intel Corporation 2012 Investor Meeting

Labels:

450mm,

5nm,

Circuit,

circuit expert,

circuit experts,

Design,

Device,

expert,

Fab,

industrial,

industry,

Manufacturing,

nm,

Process,

testify

Tuesday, May 15, 2012

Hynix Next Gen. NAND Flash

In December 2011, at the IEDM conference Hynix presented their version of the next generation of NAND flash (smaller than 20nm). Key developments presented: "A middle-1x nm design rule multi-level NAND flash memory cell (M1X-NAND) has been successfully developed for the first time.

1) Quad spacer patterning technology (QSPT) of ArF immersion lithography is used for patterning mid-1x-nm rule wordline (WL). In order to achieve high performance and reliability, several integration technologies are adopted, such as

2) advanced WL air-gap process,

3) floating gate slimming process, and

4) optimized junction formation scheme. And also, by using

5) new N±1 WL Vpass scheme during programming, charge loss and program speed are greatly improved."

See more details below.

Ron

A middle-1X nm NAND flash memory cell (M1X-NAND) with highly manufacturable integration technologies

Joowon Hwang, Jihyun Seo, et al., Hynix Semiconductor Inc.

5/14/2012 3:21 PM EDT

Editor’s note: This work was first presented at the 2011 IEEE International Electron Devices Meeting (IEDM) and appears here courtesy of the IEEE.

For more information about IEDM 2012 (San Francisco, CA; December 10-12), click here. A middle-1x nm design rule multi-level NAND flash memory cell (M1X-NAND) has been successfully developed for the first time.

1) Quad spacer patterning technology (QSPT) of ArF immersion lithography is used for patterning mid-1x-nm rule wordline (WL). In order to achieve high performance and reliability, several integration technologies are adopted, such as 2) advanced WL air-gap process, 3) floating gate slimming process, and 4) optimized junction formation scheme. And also, by using 5) new N±1 WL Vpass scheme during programming, charge loss and program speed are greatly improved. As a result, mid-1x-nm design rule NAND flash memories has been successfully realized.

The NAND flash memory cell has been scaled down to the 2x [1,2,3] and 2y nm [4] generations aggressively. As scaling down of a cell size, many serious scaling problems were caused in 2x and 2y nm generation, however they were solved or managed by process, device, and system solutions. For further scaling down beyond 2y nm, we face new scaling limitations such as patterning limitation of ArF immersion spacer patterning technology (SPT), more severe control gate (CG) poly-Si filling problems between floating gates (FGs), and high electric field and charge loss problem between WLs. This paper describes several new advanced processes and operation schemes to overcome these problems, as shown in Table 1. As a result, M1XNAND flash cell is successfully implemented with highly manufacturable integration technologies.

Table 1: Major issues and solution of mid-1x cell technology. M1X-NAND cell process Figure 1 shows the layout of M1X-NAND flash cells. The half pitch of WL is middle-1x nm. The BL contacts are formed staggered arrangement and a string has several dummy WLs. In order to pattern middle-1x nm design rule WLs, QSPT is intensively developed to overcome limitation of ArF immersion SPT. Figure 1: Layout of Mid-1x-nm NAND (M1X-NAND) string with dummy WLs. The half pitch of WL is mid-1x-nm. As shown in Figure 2, first patterns are formed by photolithography and the two times combination of previous formed pattern and spacer are formed final patterns. Figure 2: Schematic diagram of QSPT (Quad Spacer Patterning Technology) key fabrication steps. Two times spacer patterning is used to make mid-1x patterning. The WL critical dimension (CD) of QSPT, which plays a very important role of Vth distribution factor, is precisely controlled less than 1.5% uniformity (see figure 3). QSPT is successfully adopted for mid-1x-nm design rule NAND cell patterning. Figure 3: Location dependence of WL CD variation of QSPT gate patterned NAND string. WL CD is precisely controlled under 1.5% uniformity. Figure 4 shows cross-sectional TEM micrographs of M1X-NAND cell, (a) along WL-direction, and (b) along BL-direction. Figure 4: Cross-section TEM view of the cell, (a) along WL direction, (b) along BL direction. The CGs are well patterned with middle-1x nm half pitch. The floating gate slimming process can achieve the void-free filling of CG poly-Si and wider active area CD, which can obtain large cell current. An electrical depletion in CG poly-Si is greatly suppressed by this void-free process. As a result, BL interference is successfully improved 20% compared with conventional process (see figure 5). The CG CoSi height was selected reasonably to achieve optimized gate shape and decrease WL RC delay for improvement program performance. Figure 5: The simulated results of BL interference with FG slimming scheme. BL interference can be improved to 20%. Cell performance To suppress charge loss (Q-loss) between CG and neighbor FG due to lateral high electric field during program, we have adopted an advanced CoSi-based WL air-gap process that has an air-gap portion above 50% between WLs. As shown in Figure 6(a), the electric field between CG and neighbor FG can be reduced 20% by an advanced CoSi-base WL air-gap. However, reduction electric field by WL airgap is not sufficient to prevent charge loss perfectly because of scale-down issues at mid-1x-nm cell size. So N±1 WL bias control scheme were adopted within WL air-gap. As a result we can also reduce the electric field 15% additionally (see figure 6(a)). Figure 6: (a) Electric field between CG and neighbor FG during programming. (b) 3-D e-field simulation with programmed PV3 neighbor cell. The electric field at point A can be reduced by air-gap and N±1 WL bias control. Then the advanced air-gap and N±1 WL scheme can greatly alleviate charge loss between CG and neighbor FG by decreasing electric field, as shown in Figure 7. Furthermore, as shown Figure 8, PGM speed is improved by N±1 WL scheme, because FG potential of program cell increase by cross coupling effect between WL and neighbor FG. Figure 9 shows the cell coupling ratio with and without air-gap. Cell coupling ratio can be also improved by air-gap due to reducing capacitance of WL direction. Figure 7: Improvement of charge loss with N±1 WL bias control method. Charge loss is greatly decreased to ~300mV by applying Vpass+2V to neighbor N±1 WL. Figure 8: Improvement of PGM speed with N±1 bias control method. Figure 9: Cell coupling ratio as technology shrinkage. Read current reduction is also major issue because of higher bulk doping for suppressing short channel effects in mid-1x-nm cell transistors. A new advanced junction scheme of cell and select transistor is adopted to maximize read current and reduce leakage current in unselected block (see figure 10). Figure 10: Read current with/without select Tr. junction optimization. Read current can be improved by select Tr. junction optimization. Cell Vth Distribution Figure 11 shows cell Vth distributions for the multi-level M1X-NAND cells. The Vth distributions have normal shapes and are well separated to three MLC states. This result confirms that M1X-NAND cell technology can be applied for high density MLC. Figure 11: Three-level programmed Vth distributions of M1X-NAND cells. Vth distributions are well separated to three MLC states. A highly manufacturable mid-1x-nm NAND flash memory (M1X-NAND) has been developed with new integration technologies, such as QSPT, advanced WL air gap process, floating gate slimming process, and optimized junction formation scheme, to overcome scaling limits of mid-1x-nm technology. The excellent device characteristics and reliability are achieved successfully. And also, a new N±1 WL Vpass scheme during programming has been also adopted to overcome WL-to-WL high field issue. Then, we have demonstrated a middle-1x nm-generation NAND flash memory (M1X-NAND) with high performance and reliability. References 1 K. Prall, et al., “25nm 64Gb MLC Technology and Scaling Challenge,” IEEE IEDM Technical Digest, pp. 102-103, 2010. 2. C. Lee, et al., “A Highly Manufacturable Integration Technology for 27nm a and 3bit/cell NAND Flash Memory,” IEEE IEDM Technical Digest, pp. 98-101, 2010. 3. H. Shim, et al., “Highly Reliable 26nm 64Gb MLC E2NAND (Embedded -ECC & Enhanced-efficiency Flash Memory with MSP (Memory Signal Processing) Controller,” VLSI Symp. Technical Digest, pp. 216-217, 2011. 4. K. Lee, et al., “A Highly Manufacturable Integration Technology of 20nm Generation 64Gb Multi-Level NAND Flash Memory,” VLSI Symp. Technical Digest, pp. 70-71, 2011. About the authors This article was contributed by the Flash Device Development & Advanced Process Team, R&D Division, Hynix Semiconductor Inc. The authors include J. Hwang, J. Seo, Y. Lee, S. Park, J. Leem, J. Kim, T. Hong, S. Jeong, K. Lee, H. Heo, H. Lee, P. Jang, K. Park, Myungshik Lee, S. Baik, J. Kim, H. Kkang*, M. Jang*, J. Lee*, G. Cho, J. Lee, B. Lee*, H. Jang, S. Park, J. Kim*, S. Lee, S. Aritome, S. Hong and S. Park

1) Quad spacer patterning technology (QSPT) of ArF immersion lithography is used for patterning mid-1x-nm rule wordline (WL). In order to achieve high performance and reliability, several integration technologies are adopted, such as

2) advanced WL air-gap process,

3) floating gate slimming process, and

4) optimized junction formation scheme. And also, by using

5) new N±1 WL Vpass scheme during programming, charge loss and program speed are greatly improved."

See more details below.

Ron

A middle-1X nm NAND flash memory cell (M1X-NAND) with highly manufacturable integration technologies

Joowon Hwang, Jihyun Seo, et al., Hynix Semiconductor Inc.

5/14/2012 3:21 PM EDT

Editor’s note: This work was first presented at the 2011 IEEE International Electron Devices Meeting (IEDM) and appears here courtesy of the IEEE.

For more information about IEDM 2012 (San Francisco, CA; December 10-12), click here. A middle-1x nm design rule multi-level NAND flash memory cell (M1X-NAND) has been successfully developed for the first time.

1) Quad spacer patterning technology (QSPT) of ArF immersion lithography is used for patterning mid-1x-nm rule wordline (WL). In order to achieve high performance and reliability, several integration technologies are adopted, such as 2) advanced WL air-gap process, 3) floating gate slimming process, and 4) optimized junction formation scheme. And also, by using 5) new N±1 WL Vpass scheme during programming, charge loss and program speed are greatly improved. As a result, mid-1x-nm design rule NAND flash memories has been successfully realized.

The NAND flash memory cell has been scaled down to the 2x [1,2,3] and 2y nm [4] generations aggressively. As scaling down of a cell size, many serious scaling problems were caused in 2x and 2y nm generation, however they were solved or managed by process, device, and system solutions. For further scaling down beyond 2y nm, we face new scaling limitations such as patterning limitation of ArF immersion spacer patterning technology (SPT), more severe control gate (CG) poly-Si filling problems between floating gates (FGs), and high electric field and charge loss problem between WLs. This paper describes several new advanced processes and operation schemes to overcome these problems, as shown in Table 1. As a result, M1XNAND flash cell is successfully implemented with highly manufacturable integration technologies.

Table 1: Major issues and solution of mid-1x cell technology. M1X-NAND cell process Figure 1 shows the layout of M1X-NAND flash cells. The half pitch of WL is middle-1x nm. The BL contacts are formed staggered arrangement and a string has several dummy WLs. In order to pattern middle-1x nm design rule WLs, QSPT is intensively developed to overcome limitation of ArF immersion SPT. Figure 1: Layout of Mid-1x-nm NAND (M1X-NAND) string with dummy WLs. The half pitch of WL is mid-1x-nm. As shown in Figure 2, first patterns are formed by photolithography and the two times combination of previous formed pattern and spacer are formed final patterns. Figure 2: Schematic diagram of QSPT (Quad Spacer Patterning Technology) key fabrication steps. Two times spacer patterning is used to make mid-1x patterning. The WL critical dimension (CD) of QSPT, which plays a very important role of Vth distribution factor, is precisely controlled less than 1.5% uniformity (see figure 3). QSPT is successfully adopted for mid-1x-nm design rule NAND cell patterning. Figure 3: Location dependence of WL CD variation of QSPT gate patterned NAND string. WL CD is precisely controlled under 1.5% uniformity. Figure 4 shows cross-sectional TEM micrographs of M1X-NAND cell, (a) along WL-direction, and (b) along BL-direction. Figure 4: Cross-section TEM view of the cell, (a) along WL direction, (b) along BL direction. The CGs are well patterned with middle-1x nm half pitch. The floating gate slimming process can achieve the void-free filling of CG poly-Si and wider active area CD, which can obtain large cell current. An electrical depletion in CG poly-Si is greatly suppressed by this void-free process. As a result, BL interference is successfully improved 20% compared with conventional process (see figure 5). The CG CoSi height was selected reasonably to achieve optimized gate shape and decrease WL RC delay for improvement program performance. Figure 5: The simulated results of BL interference with FG slimming scheme. BL interference can be improved to 20%. Cell performance To suppress charge loss (Q-loss) between CG and neighbor FG due to lateral high electric field during program, we have adopted an advanced CoSi-based WL air-gap process that has an air-gap portion above 50% between WLs. As shown in Figure 6(a), the electric field between CG and neighbor FG can be reduced 20% by an advanced CoSi-base WL air-gap. However, reduction electric field by WL airgap is not sufficient to prevent charge loss perfectly because of scale-down issues at mid-1x-nm cell size. So N±1 WL bias control scheme were adopted within WL air-gap. As a result we can also reduce the electric field 15% additionally (see figure 6(a)). Figure 6: (a) Electric field between CG and neighbor FG during programming. (b) 3-D e-field simulation with programmed PV3 neighbor cell. The electric field at point A can be reduced by air-gap and N±1 WL bias control. Then the advanced air-gap and N±1 WL scheme can greatly alleviate charge loss between CG and neighbor FG by decreasing electric field, as shown in Figure 7. Furthermore, as shown Figure 8, PGM speed is improved by N±1 WL scheme, because FG potential of program cell increase by cross coupling effect between WL and neighbor FG. Figure 9 shows the cell coupling ratio with and without air-gap. Cell coupling ratio can be also improved by air-gap due to reducing capacitance of WL direction. Figure 7: Improvement of charge loss with N±1 WL bias control method. Charge loss is greatly decreased to ~300mV by applying Vpass+2V to neighbor N±1 WL. Figure 8: Improvement of PGM speed with N±1 bias control method. Figure 9: Cell coupling ratio as technology shrinkage. Read current reduction is also major issue because of higher bulk doping for suppressing short channel effects in mid-1x-nm cell transistors. A new advanced junction scheme of cell and select transistor is adopted to maximize read current and reduce leakage current in unselected block (see figure 10). Figure 10: Read current with/without select Tr. junction optimization. Read current can be improved by select Tr. junction optimization. Cell Vth Distribution Figure 11 shows cell Vth distributions for the multi-level M1X-NAND cells. The Vth distributions have normal shapes and are well separated to three MLC states. This result confirms that M1X-NAND cell technology can be applied for high density MLC. Figure 11: Three-level programmed Vth distributions of M1X-NAND cells. Vth distributions are well separated to three MLC states. A highly manufacturable mid-1x-nm NAND flash memory (M1X-NAND) has been developed with new integration technologies, such as QSPT, advanced WL air gap process, floating gate slimming process, and optimized junction formation scheme, to overcome scaling limits of mid-1x-nm technology. The excellent device characteristics and reliability are achieved successfully. And also, a new N±1 WL Vpass scheme during programming has been also adopted to overcome WL-to-WL high field issue. Then, we have demonstrated a middle-1x nm-generation NAND flash memory (M1X-NAND) with high performance and reliability. References 1 K. Prall, et al., “25nm 64Gb MLC Technology and Scaling Challenge,” IEEE IEDM Technical Digest, pp. 102-103, 2010. 2. C. Lee, et al., “A Highly Manufacturable Integration Technology for 27nm a and 3bit/cell NAND Flash Memory,” IEEE IEDM Technical Digest, pp. 98-101, 2010. 3. H. Shim, et al., “Highly Reliable 26nm 64Gb MLC E2NAND (Embedded -ECC & Enhanced-efficiency Flash Memory with MSP (Memory Signal Processing) Controller,” VLSI Symp. Technical Digest, pp. 216-217, 2011. 4. K. Lee, et al., “A Highly Manufacturable Integration Technology of 20nm Generation 64Gb Multi-Level NAND Flash Memory,” VLSI Symp. Technical Digest, pp. 70-71, 2011. About the authors This article was contributed by the Flash Device Development & Advanced Process Team, R&D Division, Hynix Semiconductor Inc. The authors include J. Hwang, J. Seo, Y. Lee, S. Park, J. Leem, J. Kim, T. Hong, S. Jeong, K. Lee, H. Heo, H. Lee, P. Jang, K. Park, Myungshik Lee, S. Baik, J. Kim, H. Kkang*, M. Jang*, J. Lee*, G. Cho, J. Lee, B. Lee*, H. Jang, S. Park, J. Kim*, S. Lee, S. Aritome, S. Hong and S. Park

Labels:

Circuit,

circuit expert,

circuit experts,

Design,

Device,

expert,

Flash,

floating gate,

industrial,

manufacture,

Manufacturing,

memory testify,

NAND,

nm,

Process

Friday, May 11, 2012

Intel: Installed Base Adv. for Tablets, Wibdow8 vs. Arm processor

A key benefit of legacy, installed base (see below).

Ron

http://m.computerworld.com/s/article/9227066/Intel_CEO_Otellini_calls_out_ARM_on_Windows_8_tablets

Intel CEO Otellini calls out ARM on Windows 8 tablets Otellini says Intel chips are better at supporting legacy apps on Windows 8 By Agam Shah May 10, 2012 02:59 PM ET IDG News Service -Intel CEO Paul Otellini on Thursday said that the company has an advantage over its rival ARM on Windows 8 for tablets because of decades of developing x86 chips that support the Windows operating system. "We think it's a differentiator," said Otellini at the company's investor meeting in Santa Clara, California. "We have the advantage of the incumbency, the legacy support."

Intel's only competitor in the Windows 8 tablet market is ARM, whose processors ship in most tablets today. ARM may have an entry point to the Windows tablet market, but faces a tough road ahead considering Intel's history with Windows, Otellini said. Windows grew up on x86 chips, but Microsoft is now also releasing Windows for the ARM architecture to make a dent into the tablet market. The upcoming Windows 8 OS will have a touch-based user interface and will come in three versions --Windows RT for ARM, and Windows 8 and Windows 8 Pro for x86 chips.

Intel plans to offer a new low-power Atom chip code-named Clover Trail, which will be released at the time of Windows 8 later this year. Otellini said PC makers are designing 20 Windows 8 tablets based on Intel chips. No ARM-based device makers have publicly announced Windows tablets, though Microsoft is working with ARM-based chip makers Nvidia, Qualcomm and Texas Instruments to bring Windows 8 compatibility to tablets and PCs. Playing the application compatibility card, Otellini said tablets with Intel's upcoming chips will support older applications written for previous versions of Windows, which is important for CIOs. "There's going to be some compatibility issues for other architectures," Otellini said.ust by pressing one button on a tablet, users will be able to jump into legacy Windows mode for those who need an older user interface, Otellini said. The Windows 8 tablets on Intel chips provide a snappy response, Otellini said.

Many application compatibility issues have been raised in the past. Intel last year claimed that legacy x86 applications would not work on Windows on ARM, a claim that was shot down by Microsoft. However, Microsoft later said that Windows on ARM would not be able to run or port existing x86 applications. Microsoft is trying to raise the appeal of Windows on ARM by bundling basic Office applications --collectively called Office 15 --with versions of Windows RT. Microsoft Office will not be included with Windows 8 or Windows 8 Pro. There are also hardware compatibility issues at stake. For example, older printers and cameras may not work with Windows on ARM devices as drivers are currently compatible only with x86 chips, and companies may be unwilling to rewrite drivers for ARM.

Intel also hopes to bring tablet features such as touchscreens to its upcoming class of thin-and-light laptops called ultrabooks. Top PC makers expect to release ultrabooks based on Windows 8 in the future. ARM could not immediately respond when asked about Otellini's comments. Agam Shah covers PCs, tablets, servers, chips and semiconductors for IDG News Service. Follow Agam on Twitter at @agamsh. Agam's e-mail address is agam_shah@idg.com

Thursday, May 10, 2012

Smartphone Components Cost; NAND Flash, Display, DRAM

|

| Smart phone components Source: Gartner |

It is interesting that semiconductor memory chips are the largest portion of smart phone cost (see below).

This is another proof of the growth of the flash market vs. DRAM memory. Dram memory is only $8-10 while Flash is $20-22. (See more at Simon Sze - Inventor of Floating Gate Non Volatile Memory and in March 16,2012 blog When will Flash Memory Market be 2x of DRAMs )

Ron

What’s Costliest Part of Smartphone? Hint: It’s Not the Display

By Olga Kharif View ProfileEmailTwitter

http://go.bloomberg.com/tech-blog/2012-05-09-whats-costliest-part-of-smartphone-hint-its-not-the-display/

May 9, 2012 8:08 PM EDT

Posted in Android, Apple, Mobile, Posts

0 Comments inShare.14PrintEmailNomura Equity Research recently released its “2012 Smartphone Guide,” which offers a graphical look at the components that go into phones and their providers’ market shares. More than 25 parts are needed to make a modern smartphone.

What were the interesting takeaways?

The display has been seen as the costliest part of the phone. Not so today, according to Nomura. NAND flash memory costs between $20 and $22 per device on average, as compared with $18 to $20 for the display. That’s good news for memory suppliers Samsung Electronics, Toshiba, SanDisk and Micron Technology. The NAND’s heftier price tag comes as phonemakers like Apple and Samsung increase the amount of memory in their devices.

While Qualcomm is the mobile chip market leader with a 24 percent share, followed by Texas Instruments Inc. with 12 percent, third place is shared by two vendors: STMicroelectronics NV and Taiwanese company MediaTek Inc. — the low-cost supplier that’s been gaining steam. At 9 percent, MediaTek’s share of the mobile semiconductor market last year was higher than that of Intel, Broadcom or Samsung.

Nomura’s graphical guide is big, so we broke it into different chunks below. You can also view the complete chart.

Labels:

bit,

Circuit,

digital camera,

DRAM,

expert,

Flash,

floating gate,

floating-gate,

gate,

Memory,

Memory chip,

NAND,

non volatile,

non-volatile,

nonvolatile,

NVM,

testify,

testimony,

transistor

Wednesday, May 9, 2012

Nvidia #1 at TSMC Fab? Nvida has Priority for 28nm capacity

"TSMC has given priority to Nvidia for 28nm capacity, according to industry sources" (see below).

Complaining publicly did not hurt - see March 26, 2012 blog Nvidia: TSMC 20nm Essentially Worthless

Ron

TSMC gives priority to Nvidia for 28nm capacity

http://www.digitimes.com/news/a20120509PD211.html?mod=2

Monica Chen, Taipei; Joseph Tsai, DIGITIMES [Wednesday 9 May 2012]

Taiwan Semiconductor Manufacturing Company (TSMC) has given priority to Nvidia for 28nm capacity, according to industry sources.

Since Nvidia has been unsatisfied with TSMC's 28nm process, while the company has also not refuted rumors that the company may cooperate with Samsung Electronics or Globalfoundries, TSMC, to sooth Nvidia, has put the GPU maker on its supply priority, allowing Nvidia to be able to release its 28nm GPUs on schedule in May and June.

The same situation has also happened previously with Qualcomm, which had said it would consider outsourcing orders to other wafer foundries, and successfully gained TSMC's promise for supply priority.

With both Qualcomm and Nvidia achieving supply priority from TSMC, players that are also waiting for TSMC's 28nm capacity, are expected to be affected.

|

| Nvidia has been unsatisfied with TSMC's 28nm process Photo: Monica Chen, Digitimes file photo |

Complaining publicly did not hurt - see March 26, 2012 blog Nvidia: TSMC 20nm Essentially Worthless

Ron

TSMC gives priority to Nvidia for 28nm capacity

http://www.digitimes.com/news/a20120509PD211.html?mod=2

Monica Chen, Taipei; Joseph Tsai, DIGITIMES [Wednesday 9 May 2012]

Taiwan Semiconductor Manufacturing Company (TSMC) has given priority to Nvidia for 28nm capacity, according to industry sources.

Since Nvidia has been unsatisfied with TSMC's 28nm process, while the company has also not refuted rumors that the company may cooperate with Samsung Electronics or Globalfoundries, TSMC, to sooth Nvidia, has put the GPU maker on its supply priority, allowing Nvidia to be able to release its 28nm GPUs on schedule in May and June.

The same situation has also happened previously with Qualcomm, which had said it would consider outsourcing orders to other wafer foundries, and successfully gained TSMC's promise for supply priority.

With both Qualcomm and Nvidia achieving supply priority from TSMC, players that are also waiting for TSMC's 28nm capacity, are expected to be affected.

Tuesday, May 8, 2012

Simon Sze - Inventor of Floating Gate Non Volatile Memory

Floating Gate Non Volatile Memory is a basic building block of Flash memory (see below).

It is impressive how far non volatile memory advanced since the early 1980's. It took it a long time for non-volatile memory to gain market acceptance.

I was at the IEDM meeting in 1984 where Toshiba introduced the concept of flash NAND IC. It took more than ten years for the flash to mature and its market to grow. The first big markets were in digital camera and flash drives.

Now it looks that NAND is going to overtake DRAM volume (When will Flash Memory Market be 2x of DRAMs ).

Ron

Simon Sze and his invention of floating-gate NVM

http://www.digitimes.com/news/a20120418PD211.html?mod=0

Josephine Lien, Taipei; Jessie Shen, DIGITIMES [Tuesday 8 May 2012]

NAND flash memory is among the key components used in today's popular consumer technology products. The birth of NAND flash could be credited to two Bell Labs researchers who fabricated the world's first floating-gate nonvolatile memory (NVM) memory device. Simon Sze was one of the inventors.

Along with William Shockley's discovery of the transistor effect, and integrated circuits invented by Jack Kilby and Robert Noyce, Sze's invention with Dawon Kahng of floating-gate NVM devices was one of the major breakthroughs in semiconductor technology.

Kahng and Sze proposed the first floating gate device in 1967, around the same time when IBM invented dynamic random access memory (DRAM) cells. IBM's computer memory breakthrough drew much attention actually, Sze recalled. DRAM memory grew its adoption rapidly in PCs during the 1970s, and has become a commodity type of chip.

However, with consumer habits changing, the DRAM business is now encountering a shrinking market for traditional PCs. Sze indicated that the market for NAND flash chips had not been practically developed until the 1990s when mobile phones started to be widely used.

NAND flash is one of the NVM types, which can keep stored data when a device's power is turned off, while DRAM functions more like the "working memory" in a computer, Sze said. Both have their own expertise to satisfy different market demands.

Unlike DRAM chips that immediately replaced magnetic core chip technology as the main computer memory when first introduced, NVM memory devices were not commercialized until about 20 years after their debut, Sze observed.

Floating-gate NVM devices were introduced in 1967, and first used in end products in 1984, Sze disclosed. The memory was adopted by Nintendo in its gaming devices to automatically retain the stored information so that players can move onto the next stage, Sze said. Floating-gate devices were also first equipped into BIOS chips to speed up the boot process for PCs.

Floating-gate NVM memory started to see its wide adoption during the 1990s when demand for handsets and memory cards boomed, Sze pointed out. Memory cards using NAND flash for storing photographs began to pose a threat to the market for traditional film products, Sze added.

The popularity of Apple's i-series products does mark a turning point for NVM memory, according to Sze. The market for NAND flash memory has expanded its size big enough to challenge that of the DRAM market. According to statistics, more than 30 billion electronic products using the float-gate memory have been shipped, and the total accumulated number will top 80 billion units within the next 10 years, said Sze.

Looking forward, it is anticipated to see a new memory technology to replace floating-gate devices, Sze indicated. But the floating gate memory should maintain its presence for at least 20 years. A number of new "unified" memory devices - which come with high-speed, high-density and non-volatile features - are still in their early stages of development, Sze said.

In addition, Sze commented that the market for NAND flash will be driven by its diversified applications - from digital cameras, flash drives to smartphones, SSDs and future technology products. Demand for NAND flash will boom thanks to the memory's high density, low power, non-volatile, rewritable and small size.

Sze also suggested that the Taiwan semiconductor industry should enhance its relationship with China in order to stay competitive. The government should adopt a more open policy to attract talents and investment as the development of the island's economy and industry should not be disrupted by political issues, Sze urged.

Sze made the comments during his recent presentation at National Chiao-Tung University (NCTU), Taiwan.

|

| Simon Sze, inventor of floating-gate NVM Memory Photo: Josephine Lien, Digitimes, March 2012 |

I worked on the first commercial EEPROM (a flavor of NVM) at Intel in 1981. It was hard to explain to customers what the advantages of EEPROM were. Sales were small.

The next big advance for the non volatile memory industry was Flash NAND.

The next big advance for the non volatile memory industry was Flash NAND.

I was at the IEDM meeting in 1984 where Toshiba introduced the concept of flash NAND IC. It took more than ten years for the flash to mature and its market to grow. The first big markets were in digital camera and flash drives.

Now it looks that NAND is going to overtake DRAM volume (When will Flash Memory Market be 2x of DRAMs ).

Ron

Simon Sze and his invention of floating-gate NVM

http://www.digitimes.com/news/a20120418PD211.html?mod=0

Josephine Lien, Taipei; Jessie Shen, DIGITIMES [Tuesday 8 May 2012]

NAND flash memory is among the key components used in today's popular consumer technology products. The birth of NAND flash could be credited to two Bell Labs researchers who fabricated the world's first floating-gate nonvolatile memory (NVM) memory device. Simon Sze was one of the inventors.

Along with William Shockley's discovery of the transistor effect, and integrated circuits invented by Jack Kilby and Robert Noyce, Sze's invention with Dawon Kahng of floating-gate NVM devices was one of the major breakthroughs in semiconductor technology.

Kahng and Sze proposed the first floating gate device in 1967, around the same time when IBM invented dynamic random access memory (DRAM) cells. IBM's computer memory breakthrough drew much attention actually, Sze recalled. DRAM memory grew its adoption rapidly in PCs during the 1970s, and has become a commodity type of chip.

However, with consumer habits changing, the DRAM business is now encountering a shrinking market for traditional PCs. Sze indicated that the market for NAND flash chips had not been practically developed until the 1990s when mobile phones started to be widely used.

NAND flash is one of the NVM types, which can keep stored data when a device's power is turned off, while DRAM functions more like the "working memory" in a computer, Sze said. Both have their own expertise to satisfy different market demands.

Unlike DRAM chips that immediately replaced magnetic core chip technology as the main computer memory when first introduced, NVM memory devices were not commercialized until about 20 years after their debut, Sze observed.

Floating-gate NVM devices were introduced in 1967, and first used in end products in 1984, Sze disclosed. The memory was adopted by Nintendo in its gaming devices to automatically retain the stored information so that players can move onto the next stage, Sze said. Floating-gate devices were also first equipped into BIOS chips to speed up the boot process for PCs.

Floating-gate NVM memory started to see its wide adoption during the 1990s when demand for handsets and memory cards boomed, Sze pointed out. Memory cards using NAND flash for storing photographs began to pose a threat to the market for traditional film products, Sze added.

The popularity of Apple's i-series products does mark a turning point for NVM memory, according to Sze. The market for NAND flash memory has expanded its size big enough to challenge that of the DRAM market. According to statistics, more than 30 billion electronic products using the float-gate memory have been shipped, and the total accumulated number will top 80 billion units within the next 10 years, said Sze.

Looking forward, it is anticipated to see a new memory technology to replace floating-gate devices, Sze indicated. But the floating gate memory should maintain its presence for at least 20 years. A number of new "unified" memory devices - which come with high-speed, high-density and non-volatile features - are still in their early stages of development, Sze said.

In addition, Sze commented that the market for NAND flash will be driven by its diversified applications - from digital cameras, flash drives to smartphones, SSDs and future technology products. Demand for NAND flash will boom thanks to the memory's high density, low power, non-volatile, rewritable and small size.

Sze also suggested that the Taiwan semiconductor industry should enhance its relationship with China in order to stay competitive. The government should adopt a more open policy to attract talents and investment as the development of the island's economy and industry should not be disrupted by political issues, Sze urged.

Sze made the comments during his recent presentation at National Chiao-Tung University (NCTU), Taiwan.

Labels:

bit,

digital camera,

DRAM,

expert,

Fab,

Flash,

floating gate,

floating-gate,

gate,

Memory,

Memory chip,

NAND,

non volatile,

non-volatile,

nonvolatile,

NVM,

testify,

testimony,

transistor

Monday, May 7, 2012

First DDR4 DRAM from Micron

Micron Announces Its First Fully Functional DDR4 DRAM Module

Micron today announced development of its first fully functional DDR4 DRAM module. The company has begun sampling and has received feedback from major customers to support quick implementation for applications in 2013. Codeveloped by Nanya and based on Micron's 30-nanometer (nm) technology, the 4-gigabit (Gb) DDR4 x8 part is the first piece of what is expected to be the industry's most complete portfolio of DDR4-based modules, which will include RDIMMs, LRDIMMs, 3DS, SODIMMs and UDIMMs (standard and ECC). It is expected that the enterprise and micro-server markets will take full advantage of the new features and specifications designed into DDR4, accelerating early adoption of the technology. In addition, the fast-growing ultrathin client and tablet markets will also benefit from new opportunities enabled by the power savings and performance features of Micron's DDR4. As JEDEC finalizes the DDR4 specifications, Micron is positioned to quickly become fully compliant with its 30nm 4Gb DDR4 part. Full sampling to key partners began earlier this year and volume production is planned for 4Q12. Sounds like we might be seeing some DDR4 platforms in 2013!

"With the JEDEC definition for DDR4 very near finalization, we've put significant effort into ensuring that our first DDR4 product is as JEDEC-compatible as it can be at this final stage of its development," said Brian Shirley, vice president for Micron's DRAM Solutions Group. "We've provided samples to key partners in the market place with confidence that the die we give them now is the same die we will take into mass production."Additional information on DDR DRAM Memory

Labels:

3DS,

Circuit,

circuit expert,

circuit experts,

DDR,

ddr4,

Design,

DRAM,

ECC,

expert,

LRDIMM,

manufacture,

Manufacturing,

Memory,

moudle,

RDIMMs,

SODIMM,

testify,

testimony,

UDIMM

Friday, May 4, 2012

Apple's A5 Die Shrink, Improve Battery Life, Cut Cost

A teardown of a new iPad reveals a shrunk SoC die (see below). In second half of 2011 an iPad's processor was made in the 45nm manufacturing process, while the current iPad seems to use a 32nm process.

The iPad 2,4 Review: 32nm Brings Better Battery Life

by Anand Lal Shimpi on 5/4/2012 12:50:00 AM

http://www.anandtech.com/show/5789/the-ipad-24-review-32nm-a5-tested

When Apple launched the 3rd generation iPad (as the new iPad), it also dropped the price of the entry-level 16GB WiFi iPad 2 to $399. Apple's products tend to hold their values exceptionally well, so this two-tablet strategy made sense. Apple also proved the success of discount-the-previous-gen strategy with its iPhone line, where you can now buy current, n-1 and n-2 generations of iPhones at prices separated by $100.

What's different with the $399 iPad 2 is that Apple used it as a vehicle to introduce a new hardware platform, or more specifically, a new SoC.

When Apple launched the 3rd generation iPad (as the new iPad), it also dropped the price of the entry-level 16GB WiFi iPad 2 to $399. Apple's products tend to hold their values exceptionally well, so this two-tablet strategy made sense. Apple also proved the success of discount-the-previous-gen strategy with its iPhone line, where you can now buy current, n-1 and n-2 generations of iPhones at prices separated by $100.

What's different with the $399 iPad 2 is that Apple used it as a vehicle to introduce a new hardware platform, or more specifically, a new SoC.

The 32nm HK+MG Apple A5 SoC

Prior to the new iPad announcement there were three versions of the iPad 2:

iPad 2,1 iPad 2,2 iPad 2,3 iPad 2,4

A5 SoC 45nm LP 45nm LP 45nm LP 32nm LP

Connectivity WiFi WiFi + GSM WiFi + CDMA WiFi

Connectivity WiFi WiFi + GSM WiFi + CDMA WiFi

The 2,1 was WiFi-only, the 2,2 was GSM and the 2,3 was CDMA. The new addition to the family is the iPad 2,4. The 2,4 replaces the original iPad 2,1. It's also only available in a single capacity.

There's no known way to tell whether you're getting an iPad 2,4 vs. the older iPad 2,1 without opening the box. The 2,4 unit I ended up with was made in China, ruling out manufacturing region as a way of telling. The external box looks identical, as does the device itself.

The newer iPad 2,4 units should come with iOS 5.1 preloaded, while any older iPad 2,1 stock may have 5.0.1 or older. But the most accurate way to tell is by looking at what a utility like Geekbench will tell you about the hardware:

This particular iPad 2,4 sample came from Best Buy, and several attempts to find one elsewhere came up short. All indications seem to point to the iPad 2,4 being relatively rare, which makes sense considering what's inside it.

Although the iPad 2,1 and its 3G brethren all used a 45nm Apple A5 SoC, the iPad 2,4 uses a die-shrunk 32nm version. The performance remains the same, but the die is much smaller. This isn't however just a normal die shrink, as Apple is using Samsung's 32nm high-k + metal gate LP transistors for this new A5 die. Intel was first to make the HK+MG transition back at 45nm in 2007 and correctly predicted that no one else would make the move until 32nm at the earliest.

Transistors are amazingly complex to fully understand, but at a high level they're quite simple. Imagine a transistor as a silicon based switch. When on, current flows, and when off, current stops flowing. The smaller you make a transistor, the more likely it is to misbehave. If current flows while the transistor is off, you waste power. This is known as leakage current and can come from a number of sources.

One such source is the gate oxide/gate dielectric, a particularly thin part of modern day transistors - on the order of a handful of atoms thick. Thinning the gate dielectric is desirable up to a certain point, after which the dielectric simply leaks too much power. Switching to a different material here, specifically one with a higher dielectric constant (a higher k-value), can significantly reduce leakage current and mitigate this issue. This is exactly what the first part of Samsung's 32nm high-k + metal gate process does.

The second half of the new process is the introduction of a metal gate electrode. Switching from a polysilicon to a metal gate electrode results in higher drive current by elimination of a region of depleted conducting carriers between the gate electrode and gate dielectric.

The combination of these two innovations results in less wasted current and more efficient current delivery, which in turn can give us a more power efficient chip. It's a net win. It makes manufacturing more complex, and there's definitely a learning curve to implementing it, but after you get over that hurdle it becomes just another part of the process.

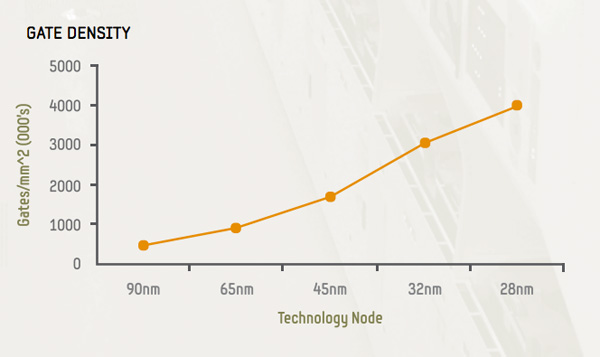

The More Cost Effective Die

Traditionally the move to a smaller process node brings about an increase in transistor density. As transistors get smaller, you can fit more of them into the same space (or the same number into a smaller space). It's this basic principle that makes Moore's Law work. If you can keep shrinking transistor size by about 50% every two years, you'll theoretically be able to double transistor count at the same cost every two years (or cut cost in half every two years). In practice it doesn't work this well. Newer processes are always more expensive than their predecessors initially and logic scaling is never perfect.

It's rare these days that we actually see a pure die shrink anymore. With Intel's tick-tock model we almost always see increases in functionality to accompany each process node shift. In the case of Ivy Bridge, we actually saw a significant increase in transistor count thanks to an improved GPU. With Apple's 32nm A5 however, we truly end up with a die shrunk version of the 45nm A5 SoC. About the only part of the computing world where we see these pure shrinks is in the console space where performance doesn't have to go up within a generation, but cost must go down.

The original 45nm A5's die measured approximately 122mm^2. The new 32nm A5 has a surface area of only 69mm^2. That's actually amazingly good scaling at 57% of the old die size, as perfect scaling from 45nm to 32nm would be around 50.5%.

Assuming Apple could make full use of a 300mm wafer (which it can't, wafers are round, chips are rectangular at best so there are some unusable chips), Samsung could deliver 579 45nm A5 die to Apple. The move to 32nm would give Apple 75% more die per wafer at 1015 chips. Again both of these numbers are over estimates as they assume full usage of the surface area of a wafer as well as 100% yields, but you can see the benefit of a smaller die. As long as wafer costs increase by a factor less than the 75% increase in number of die per wafer, Apple can effectively reduce SoC cost by going this route.

These ARM based SoCs are already fairly cheap - all selling well below $30 (many around $15) - so there's not a whole lot of cost savings here. On a product like the $399 iPad 2, where Apple needs to do its best to maintain margins while holding onto (and growing) market share, every last dollar matters.

There's another motivation for Apple however. Just as with any good microprocessor company, its best to introduce a new process technology on a known architecture. It's also a good idea to introduce a new process technology on lower volume products. The combination of both of these minimize risk. Should there be something wrong with the new process, introducing a new architecture on it just means you now have two very complex things to debug - the process technology and the chip's architecture. Should the new process not yield very well initially, you'd be similarly screwed if you were depending on it for your highest volume parts.